# PCI Express Bridge LSIのご紹介 AAE-B04

株式会社アバールデータ

### **Agenda**

- ●特長

- ●概略仕様

- 各機能の説明

- ●システム構築例

- 転送モードの説明

- ●性能

- 測定結果

- 初期化ツール

- ●搭載ボードのご紹介

- APX-742/AXM-741/APX-3312製品

- ●まとめ

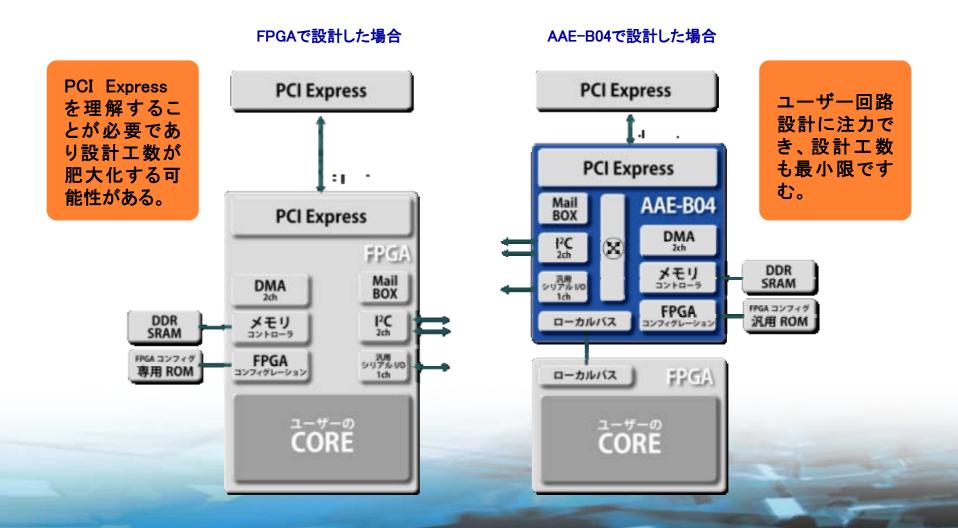

### 特長 I PCI Expressを意識せずにアドインカード設計可能

### 特長 II 様々なエンドポイントIO

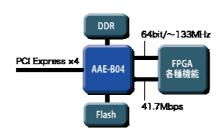

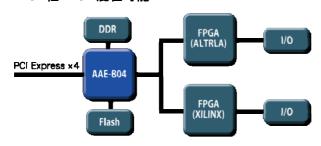

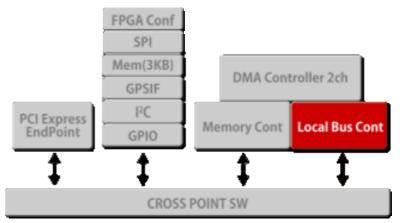

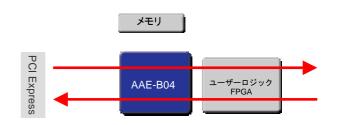

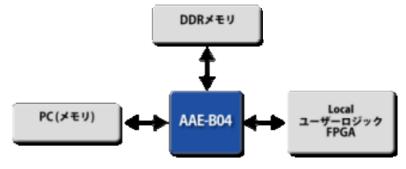

#### 基本構成

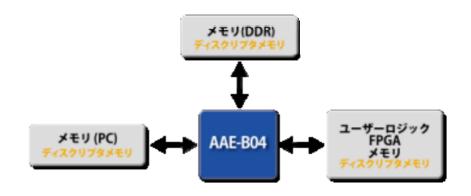

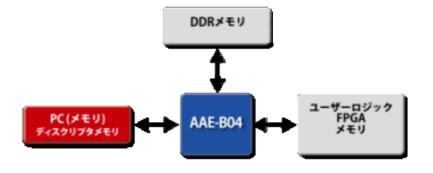

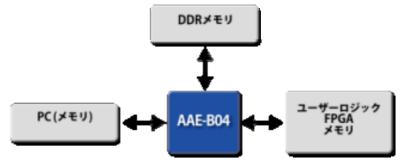

AAE-B04を中心とした基本的な構成。

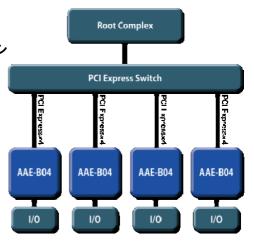

#### エンドポイントシステム

大規模な高速データ転送システム

#### 異なる機能のFPGAが混在

コンフィギュレーション機能はALTERA / XILINX / LATTICE社FPGA混在可能

#### PCI Express x8システム

X8のカード構成。

PCI Express x4 AAE-804 FPGA AAE

#### インテリジェントIO

CPUを搭載した構成。 FPGAのゲート数に余裕 があればソフトCPU。

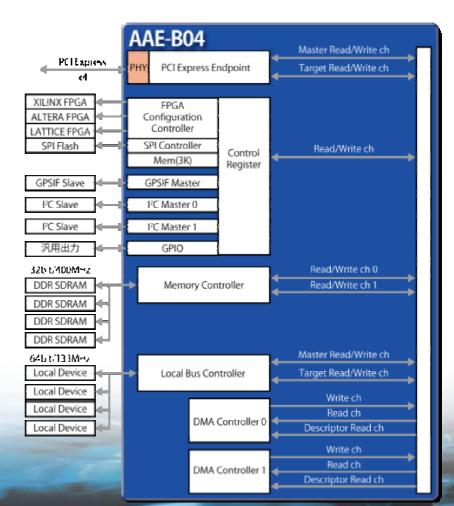

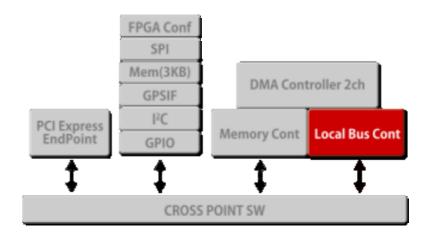

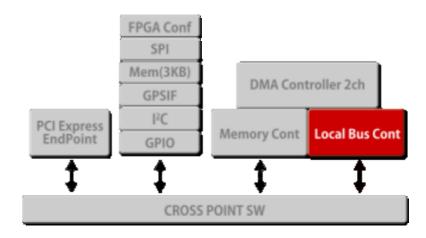

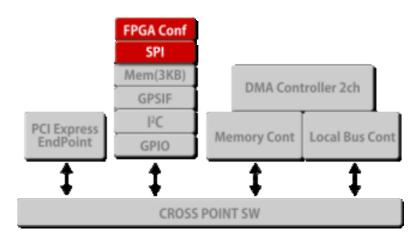

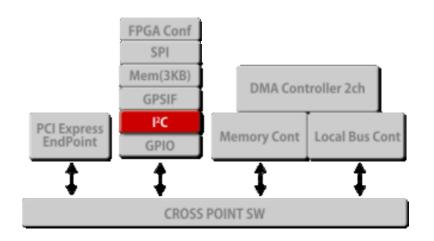

## 特長皿 PCI Expressを最大限に

- PCI-Express Specification Rev 1.0a ×4に対応

- 高速なLocal Bus: 64bit/133MHz

- 最大1GByteの大容量DDRメモリコントローラ

- DMAコントローラを2チャンネル搭載

- XILINX社、ALTERA社、Lattice社製のFPGAコンフィグレーション機能

- 最大64MByteのSPI Flashメモリコントローラ

- 8bitの汎用入出力を搭載 (GPIO)

- 2chのI2Cバスマスターを搭載

- 汎用シリアルバス搭載 (GPSIF)

- 最小アクセスレイテンシの3KByteメモリ内蔵

### 概略仕様

#### ■ AAE-BO4 の主な仕様

| ■ AAC-DU→ V王徳江塚         |                      |                                                                                                       |  |  |

|-------------------------|----------------------|-------------------------------------------------------------------------------------------------------|--|--|

| PCI Express Endpoint    | 規格                   | PCI ExpressTM Base Specification Revision 1.0a                                                        |  |  |

|                         | レーン数                 | 4 レーン                                                                                                 |  |  |

|                         | Virtual Channel (VC) | VC0のみ(1つ)                                                                                             |  |  |

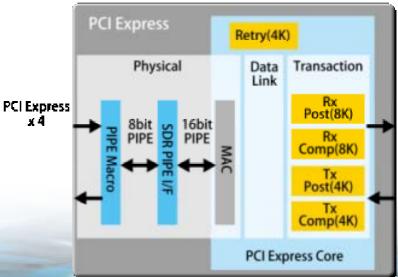

|                         | バッファサイズ              | 受信系:Posted / Completion Data:各 BKByte<br>送信系:Posted / Completion Data / Retry:各 4KByte                |  |  |

|                         | Maximum Payload Size | 1KByte                                                                                                |  |  |

| 高速メモリ I/F               | 対応メモリ                | DDR200~400<br>容量:128Mbit~1Cbit (メモリチップ辺り)<br>16MByte~1GByte (総容量)                                     |  |  |

|                         | バス幅                  | 32bit                                                                                                 |  |  |

|                         | データ帯域                | 0.8~ 1.6GByte/sec(ピーク性能)                                                                              |  |  |

|                         | 先読みメモリ               | 512Byte × 4                                                                                           |  |  |

| Local I/F               | 信号レベル                | 2.5V-LVTTL Single End                                                                                 |  |  |

|                         | バス幅                  | 64bit                                                                                                 |  |  |

|                         | バスクロック               | 133MHz(MAX)                                                                                           |  |  |

|                         | データ帯域                | 1.06GByte/Sec(ピーク性能)                                                                                  |  |  |

| FPGA Configuration Port | 対応モード                | ALTERA 社 FPGA 向け:PS Mode<br>XILINX 社 FPGA 向け:Slave Serial Mode<br>Lattice 社 FPGA 向け:Slave Serial Mode |  |  |

| SPI Memory Port         | 対応メモリ                | 品種:SPI Flash Memory<br>容量:16Kbit~128Mbit (メモリチップ辺り)<br>2KByte~64MByte (総容量)                           |  |  |

| その他機能                   | 汎用入出力 (GPIO)         | 8 bit                                                                                                 |  |  |

|                         | 汎用シリアルバス (GPSIF)     | 1 Port (5Mbps~41.7Mbps)                                                                               |  |  |

|                         | PCバス                 | 2 Port                                                                                                |  |  |

| 一般仕様                    | Package              | 672pin EPBGA( ☐ 27mm, 1mm-pitch)                                                                      |  |  |

|                         | 動作周囲温度               | 0 ~ 70°C                                                                                              |  |  |

|                         | 電源入力                 | +3.3V 20(mA) MAX<br>+2.5V 415(mA) MAX<br>+1.2V 2.2(A) MAX                                             |  |  |

### 概略仕様 PCI Express

- •PCI Express Rev 1.0a準拠

- ・デバイスタイプ: PCI Express Endpoint

- ・レーン数:1~4レーン

- •Max Payload Size:128、256、512、1024Byteをサポート

- ・高速なデータ転送を実現

理論転送速度:1GByte/秒(最大ピーク値)

実効転送速度(DMA使用時、弊社測定環境において)

Local Bus to System Memory: 890MByte/秒

System Memory to Local Bus: 810MByte/秒

- ·MSI割り込み対応

- Advanced Error Reporting対応

- ・レーン極性反転(Polarity Inversion)サポート

- ・レーン順入替(Lane Reversal)機能サポート

### 概略仕様 Local Bus

●FPGAに実装が容易なシンプルプロトコル

●信号レベル: 2.5V LVTTL

●データ帯域:1.06GByte/Sec

●バス幅: 64bit

●クロック: 133MHz(max)

●5出力のクロックドライバ内蔵

(出力周波数範囲:25MHz~133MHz)

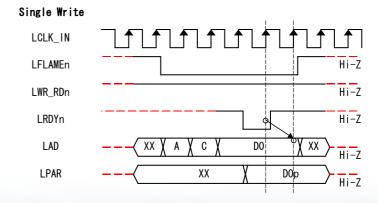

## 概略仕様 Local Bus I (基本プロトコル)

アドレス・コマンド・データの3フェーズで構成

アドレスフェーズマスタがアドレスを出力

コマンドフェーズ ・マスタがコマンドを出力

データフェーズ ・データソースがデータを出力

#### コマンドフォーマット

| bit  | 3124                   | 23          | 2217 | 160              |

|------|------------------------|-------------|------|------------------|

| info | Byte<br>Enable<br>[70] | 64bit Cycle | -    | Pay Load<br>Size |

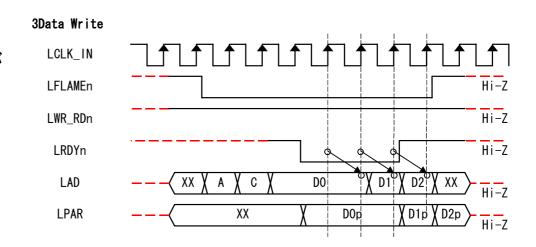

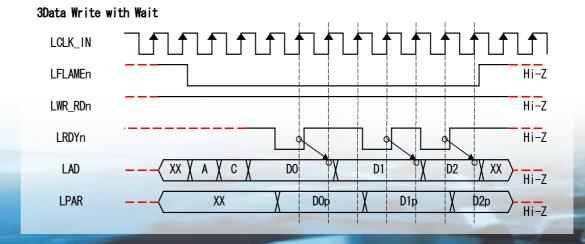

## 概略仕様 Local Bus Ⅱ (Write Timing)

Write時のデータフェイズではマスターにより常に有効なデータがLAD上に出力され、ターゲットによりLRDYn信号がアサートされた次のクロックサイクルでデータが転送されます。

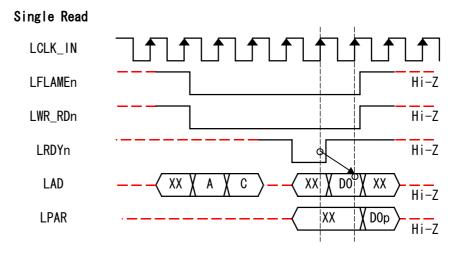

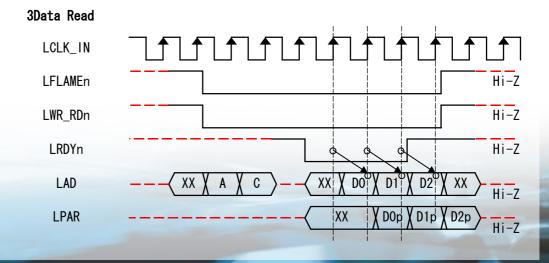

## 概略仕様 Local Bus Ⅲ (Read Timing)

Read 時のデータフェイズでは LADが、ターゲットにより出力 され、LRDYn 信号がアサート された次のクロックサイクルで データが転送されます。

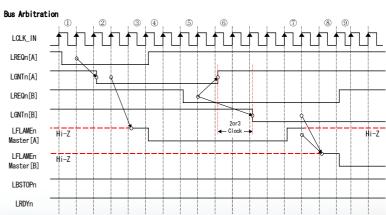

### 概略仕様 Local Bus IV(アービトレーション)

バスアービトレーションはLREQn、LGNTn、LFLAMEn、LBSTOPn、LRDYn信号を使用

- ・マスタはLREQn信号によりバス権を要 求

- アービタはLGNTn信号によりバス権を 与える

- バス権を与えられたマスタは、LFLAMEn、 LBSTOPn、LRDYn信号が全てネゲートされている時のみバスを使用開始可能

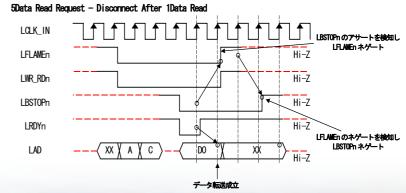

### 概略仕様 Local Bus V(サイクル中断)

- ①複数マスタが同時にバスを使用したい時

- ②ターゲットがマスタの要求した処理をすぐに実行出来ない時に使用する。

マスタ主導のサイクル中断 最初に要求した転送サイズ到達前にLFAMEn 信号をネゲートする

ターゲット主導のサイクル中断 BSTOPn信号をアサートする。

#### 注意事項

- a) PCI Expressからの要求を長時間実行しない事は避ける CPU等から、発行された要求を長時間実行出来ないと、 CPUまたはチップセットがハングアップする可能性があります。

- b) BSOTPn信号アサート時は必ず中断処理を実行する BSTOPnがアサートされた際、相手側のマスタは必ずサイクル を中断する必要があります。 (AAE-B04にはBSTOPnの出力設定があります。)

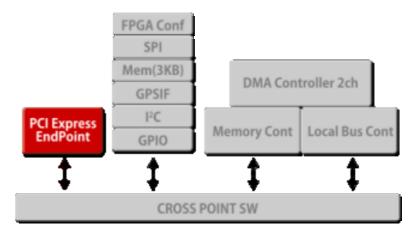

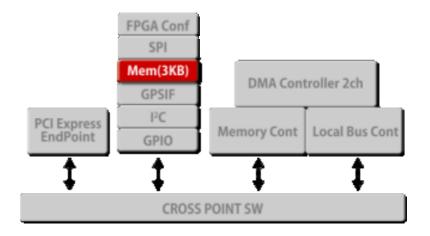

FPGA Conf

SPI

Mem(3KB)

GPSIF

PCI Express

EndPoint

GPIO

Memory Cont

Local Bus Cont

CROSS POINT SW

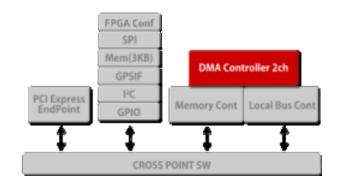

### 概略仕様 DDR SDRAMコントローラ

MemoryコントローラはDDRメモリ及び先読み キャッシュの制御を行っています。"先読み/ラ イトスルーキャッシュ"を4系統搭載して、読み 出しの高速化を計っています。 PCI Express EndPoint GPIO

CROSS POINT SW

FPGA Conf

SPI

DMA Controller 2ch

DMA Controller 2ch

Local Bus Cont

FIFOモード時は、メモリ全体がFIFOとして扱えるよう制御を行います。また、DMA コントローラと連携し、FIFOのフロー制御を行います。

#### 使用可能なDDR Memory

| 容量   | 128M~1Gbit/Chip                                                |

|------|----------------------------------------------------------------|

| 総容量  | 16MByte(min) →128Mbit 32bit幅×1個<br>1GByte(Max) →1Gbit 8bit幅×8個 |

| データ幅 | 8~32bit/Chip<br>※本LSIとの接続バス幅は、必ず32bitにする必要があります。               |

| スピード | DDR200~DDR400 1Bank時<br>DDR200~DDR333 2Bank時                   |

### 概略仕様 DMAコントローラ I

DMAコントローラは、2つの異なったブロック間のデータ転送を行う機能です。本LSIには2チャンネルのDMAコントローラを内蔵しています。

以下の2つの転送モードに対応

#### **One Shot Mode**

転送元/転送先を指定して転送を行い、転送終了でDMA完了となるモードです。外部から、転送元 /転送先を転送の都度、設定を行う必要が有ります。

#### Scatter/Gather Mode

DMAの転送元/転送先/サイズ等が書かれた構造体(Descriptor)を使用し、異なった空間やアドレスに連続して転送を行うことが可能なモードです。仮想メモリを使用したOS等で、不連続なアドレス空間が転送元/転送先となる場合に有効です。

DMA転送元/転送先としては以下の領域を指定可能です。なお、同一のエリアを転送元/転送先に指定する事は禁止です。

- -PCI Bus (64bit アドレス空間指定可能)

- ·Local Bus

- DDR Memory(FIFO)

- Register

Descriptor読み出し元としては、以下の領域を指定可能です。

- PCI Bus (64bit アドレス空間指定可能)

- ·Local Bus

- DDR Memory(FIFO)

DMAの転送単位は8Byteとなります。

### 概略仕様 DMAコントローラ II (ディスクリプタ)

ディスクリプタは、転送元/転送先/サイズ等を指定する為の構造体です。

"Scatter/Gather Mode"時、DMAコントローラは、

"デスクリプタ読み出し→DMA転送"を繰り返し行います。

ディスクリプタは、32bitアドレス空間内の転送を実行可能な"Basic Descriptor"と、64bit空間をサポートした、"64bit Descriptor"の2種類が存在します。

ディスクリプタの先読みキャッシュを内蔵しており、 DMAチャンネル毎に4個のディスクリプタテーブル を先読み可能です。

通常は管理が容易なPCサイドのメインメモリにアサインされる

### 概略仕様 SPI Flashメモリコントローラ(FPGAコンフィグレーション)

SPI Flash/FPGA Configコントローラは、SPI Flashへの読み書き及び、 XILINX/Lattice/ALTERA社のFPGA コンフィグレーションを行う機能です。

使用可能なSPI Memoryは以下のとおりです。

| 容量      | 1M~128Mbit/Chip             |  |

|---------|-----------------------------|--|

| スピード    | 25Mbps(Max) ~ 0.98Mbps(Min) |  |

| Device数 | 4個(Max)                     |  |

| 電源電圧    | 3.3V                        |  |

3FF\_FFFFh

000\_0400h 000\_03FFh

000\_0000h

FPGA Configuration Data

/User Data

Chip Initialize Data

コンフィグレーション可能なXILINX/Lattice FPGAの仕様は以下のとおりです。

| 仕様     | Slave Serial Configuration            |  |

|--------|---------------------------------------|--|

| スピード   | 25Mbps(Max) ~ 0.98Mbps(Min)           |  |

| ファイル形式 | Xilinx社用 bin形式<br>Lattice社用 bit形式     |  |

| 電源電圧   | 2.5V(Configuration 系の端子のみ左記電圧で動作すれば可) |  |

コンフィグレーション可能なALTERA FPGAの仕様は以下のとおりです。

| 容量     | Passive Serial Configuration(PS)          |  |

|--------|-------------------------------------------|--|

| スピード   | 25Mbps(Max) ~ 0.98Mbps(Min)               |  |

| ファイル形式 | rbf形式                                     |  |

| 電源電圧   | 2.5V(Configuration 系の端子のみ左記電圧で動作すれば<br>可) |  |

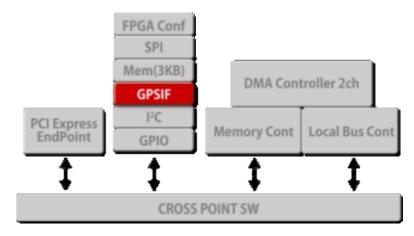

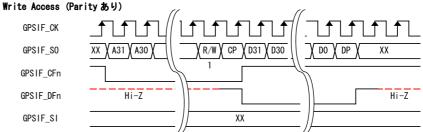

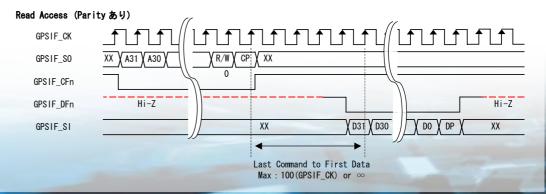

### 概略仕様 GPSIF

シンプルプロトコルのシリアルI/F 本LSIはマスターとして動作

Local Busをデータ転送で使用 している場合も、PCI側から Local側へアクセス可能な経路 を提供

動作クロックは5M~41.7MHz

### 概略仕様 I2Cバスマスタ

I<sup>2</sup>C Bus マスターポート: 2ポート

電源監視、I/Oエキスパンダなどの市販ICを接続可能。

動作クロックは10K~400Kbpsの範囲でレジスタにより設定可能です。

#### 動作クロックと、I<sup>2</sup>C仕様の対応

| 動作クロック  | I <sup>2</sup> C仕様 |

|---------|--------------------|

| 400Kbps | FAST-MODE          |

| 200Kbps | -                  |

| 100Kbps | STANDARD-MODE      |

| 50Kbps  | -                  |

| 10Kbps  | -                  |

I<sup>2</sup>Cバスの標準負荷は400pF以下

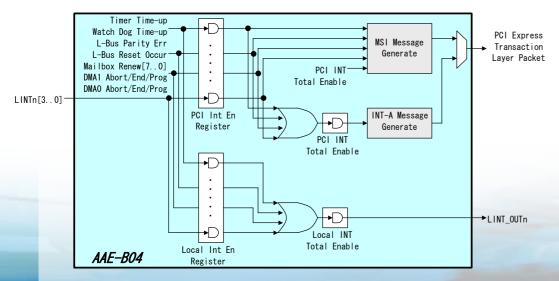

### 概略仕様 割込み

PCI/Localに対して割り込みを出力する為の機能

PCIバス割り込み:以下の2モードをサポート

- -Lagacy PCI 互換モード(INT A)

- -MSI(Massage Signaled Interrupt)モード

要因ごとにマスクビットが用意されており、割り込み許可/禁止を任意に設定可能です。

#### Legacy PCI 互換モード

INT(A,B,C,D)信号を使用した、PCI互換の割り込みモードです。本LSIからは、全ての割り込み要因の論理和が、INTAとして出力されます。 (INTB,C,Dは使用しません。)

PCI Express上では、割り込み信号が仮想化されメッセージとして伝送されます。割り込みコントローラへは、PCI Express Root Complexを経由して、通常のINTAとして通知される為、通常のPCI割り込み処理と同様に扱えます。

#### MSIモード

割り込みをメッセージ化して送る事を前提とした モードです。本モードでは、複数の割り込みメッ セージを送信する事が可能な為、割り込みを受 けた側で割り込み要因の特定を迅速に行えます。 本モードを使用する為には、ソフトウェアでの対 応が必要です。

本LSIからは8種のMSIメッセージを送信する事を要求します。但し、送信可能な割り込みメッセージの数はシステム側から設定されます。

### 概略仕様 3KBytes内蔵メモリ

PCI Express、Local Bus双方からのアクセス可能な内蔵メモリ。

- 低レイテンシでアクセス可能

- ・ステータス、メッセージ等の受け渡 しに使用

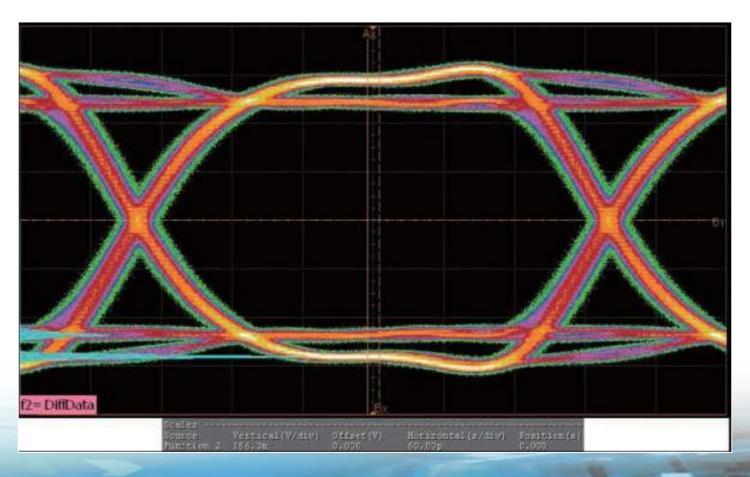

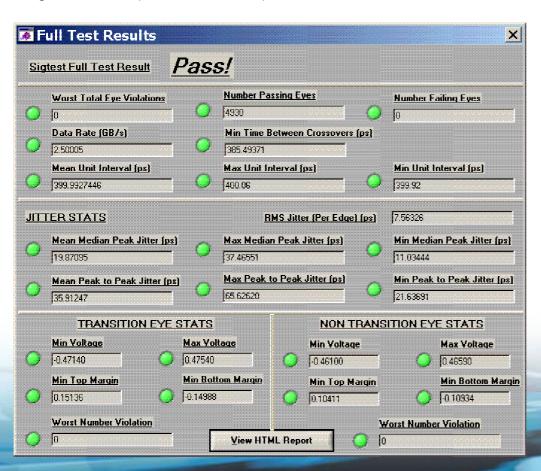

### コンプライアンステスト

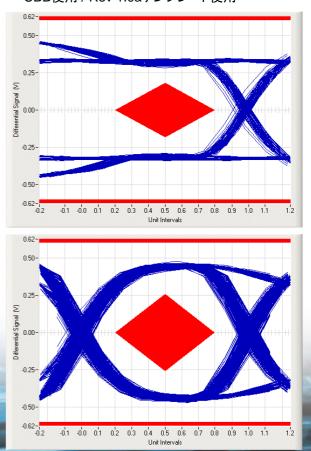

Sigtest 2.1結果 (Rev 1.0a, Lane 0)

Lane 0差動波形 CBB使用 / Rev 1.0aテンプレート使用

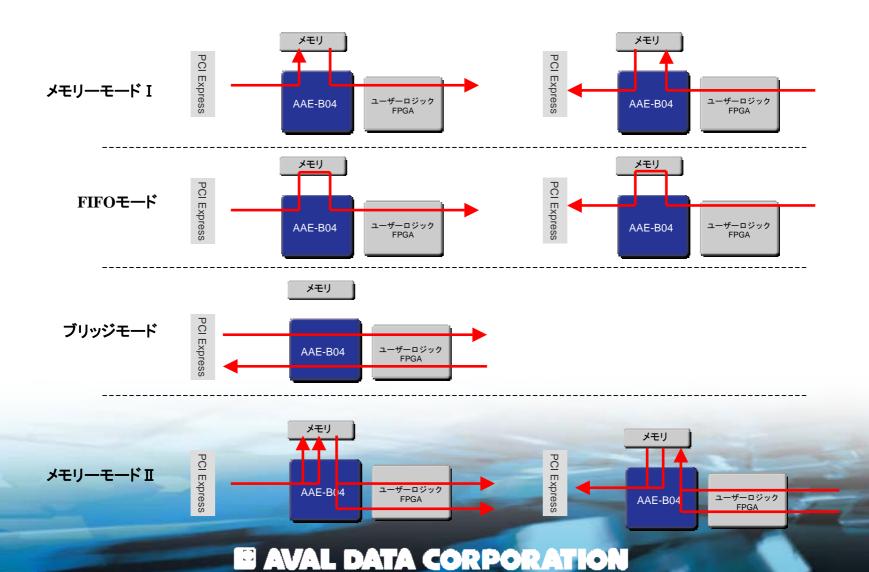

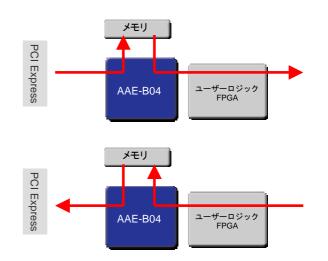

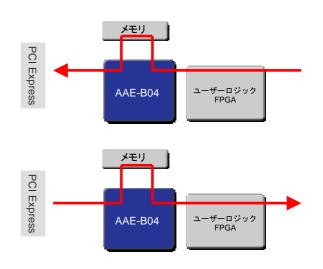

### メモリーモード I

DDRメモリを経由してPCI Expressと、Local Bus間でデータの受け渡しを行う使用方法です。

本LSIにはDMAが2chあるので、メモリ-PCI間、メモリ-Local間それぞれでDMAが使用可能です。

### FIFOモード

DDRメモリをFIFOとして利用しPCI Expressと、Local Bus 間でデータの受け渡しを行う使用方法です。

本LSIにはDMAが2chあるので、メモリーPCI間、メモリー Local間それぞれでDMAが使用可能です。また、FIFOモー ドでDMAを使用する場合、FIFOのオーバー/アンダーラ ン制御をDMAコントローラが行います。

### メモリーモードⅡ

DDRメモリを経由してPCI Expressと、Local Bus間でデータの受け渡しを行う使用方法です。メモリモード I との違いはメモリの領域を複数に分割し、それぞれ非同期に動作する事を想定している点です。

### 使用例

- ・Local Busの先には、非同期動作の複数台のカメラが 接続されている。

- ・カメラから入力された画像は非同期にDDRメモリに書き込まれる。

- ・DDRメモリに取り込まれた画像データは、順次メインメモリにコピーする。(2chのDMAを順次使用するなど)

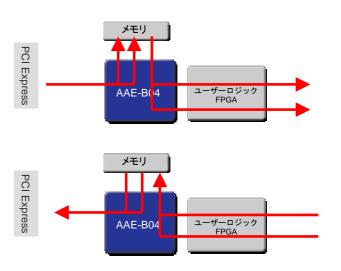

### ブリッジモード

DDRメモリを使用せず、PCI ExpressとLocal Bus間で直接データの受け渡しを行う使用方法です。

メモリを使わない為、より安価にシステム構築が可能です。

### 使用例

- ・データ帯域に十分余裕のあるシステム。

- リアルタイム性の低いデータ転送。

### 性能 パフォーマンスアップの仕掛

- ●クロスポイントスイッチ(Cross Point SW)の採用

- ●ディスクリプタ先読みキャッシュの採用

- ●DDRメモリ先読みキャッシュの採用

- ●DDRメモリFIFOモード

- ●信号によるDMA開始モード

- ●ローカルバスはパラレル/シリアル同時動作

### 性能 AAE-B04の実効値

本測定値は、AAE-B04を搭載したアバールデータ社製基板を使用し、PCI Expressのデータ転送能力を把握してして頂くために行ったもので、測定値自体を弊社で保障するものではありませんので、予めご了承載くようお願いいたします。

|    | PC      | MCH     | ICH     | MCH接続(I | Mbyte/sec) | ICH接続(M | (byte/sec) |

|----|---------|---------|---------|---------|------------|---------|------------|

|    |         |         |         | Read    | Write      | Read    | Write      |

| 1  | A社_PC   | 945G    | ICH7    | 744     | 682        | 396     | 622        |

| 2  | B社_PC1  | 955X    | ICH7    |         |            | 760     | 655        |

| 3  | B社_PC2  | 975X    | ICH7    |         |            | 759     | 640        |

| 4  | B社_PC3  | 5000X   | 631xESB | 845     | 690        | 771     | 705        |

| 5  | B社_PC4  | 5000X   | 631xESB | 845     | 690        | 771     | 705        |

| 6  | B社_PC5  | E7221   | ICH6    | 428     | 669        |         |            |

| 7  | B社_PC6  | E7230   | ICH7    | 759     | 706        | 759     | 657        |

| 8  | B社_PC7  | 3000    | ICH7    | 758     | 705        | 758     | 654        |

| 9  | B社_PC8  | E7230   | ICH7    | 745     | 690        |         |            |

| 10 | B社_PC9  | 3000    | ICH7    | 759     | 706        |         |            |

| 11 | B社_PC10 | 5000V   | 631xESB | 844     | 694        | 769     | 704        |

| 12 | B社_PC11 | 5000P   | 631xESB | 844     | 689        | 769     | 704        |

| 13 | C社_PC   | E7520   | ICH5    | 759     | 709        |         |            |

| 14 | D社_PC   | X38     | ICH9    |         |            |         |            |

| 15 | E社_PC1  | 975X    | ICH7    |         |            | 758     | 603        |

|    |         |         |         |         |            |         |            |

|    |         |         |         | Slo     | t-A        | Slo     | t-B        |

| 20 | E社_PC2  | HT-2100 | HT-1000 | 810     | 810        | 894     | 810        |

| 21 | F社_PC   | nFP3600 | nFP3050 | 760     | 800        | 760     | 800        |

PCI Expressはチップセットのクレジット数、及びペイロードサイズで転送性能が左右されます。

<u>測定条件</u> データサイズ: 2KB/Descriptor 総転送サイズ: 1MB

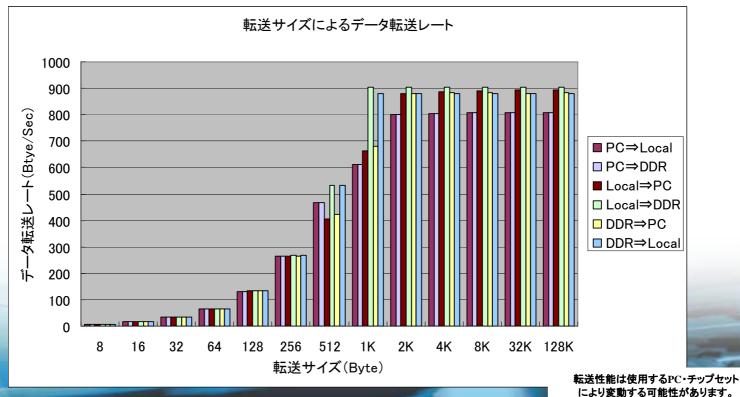

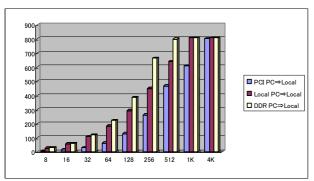

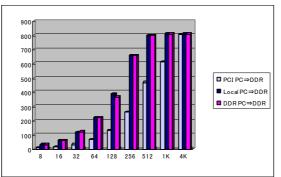

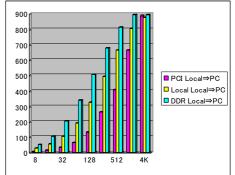

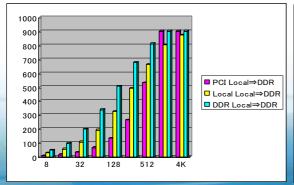

### 性能 データ転送サイズの比較(実測値)

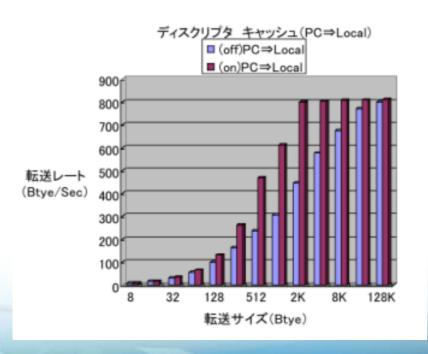

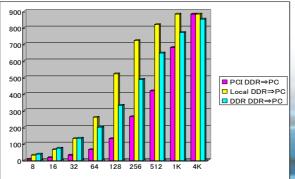

### 性能 ディスクリプタキャッシュの有効性 I (実測値)

転送サイズ 128KB以下で有効

転送性能は使用するPC・チップセット により変動する可能性があります。

**E** AVAL DATA CORPORATION

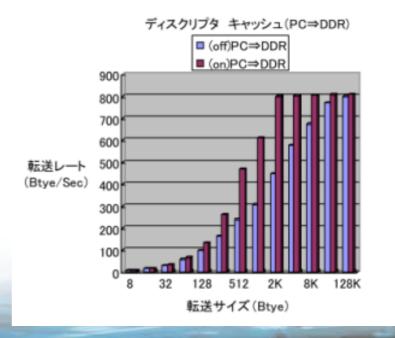

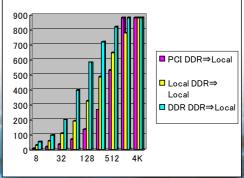

## 性能 ディスクリプタ メモリの有効性Ⅱ(実測値)

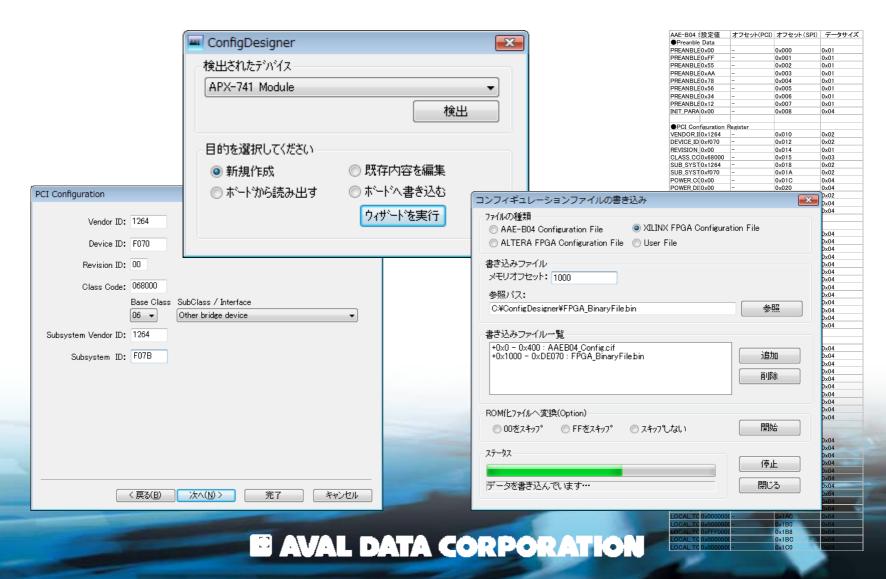

### AAE-B04初期化ツールの紹介

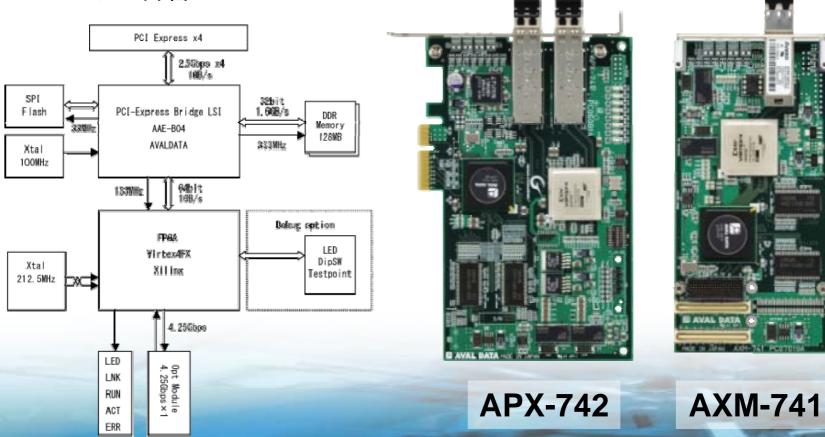

### AAE-B04搭載ボードの紹介 I アバールデータ製APX-742/AXM741

#### APX-741のブロック図

### AAE-B04搭載ボードの紹介 II アバールデータ製APX-3312

Base Configuration Camera Link規格のライン/エリアカメラに対応した PCI Express(X4)バス画像入力ボードです。カメラ2台を独立制御可能です。

カメラ電源供給を可能とするPoCL規格にも対応しており、エリア/ ライン問わず幅広いカメラに接続できます。サブパネルにて外部トリ ガ及びエンコーダ入力やストロボタイミング出力等をサポートしてお り、システム構築における周辺機器への接続も考慮した製品です。

#### ■ APX-3312の主な仕様

| 対応カメラ  | CameraLink モノクロ / カラー<br>エリア / ラインカメラ     |                                              |  |

|--------|-------------------------------------------|----------------------------------------------|--|

| 画像入力   | Base Configuration<br>20 ~ 85MHz<br>24bit |                                              |  |

| 同層出力   | カメラ制御信号                                   | CC1 ~ CC4                                    |  |

|        | 汎用出力                                      | 2ch、TTレオープンコレクタ(ストロボタイ<br>ミング出力としても可)        |  |

| 向無入力   | 外部トリガ                                     | TTL/オープンコレクタ/推動信号 RS-422                     |  |

|        | エンコーダ                                     | 差動信号 RS-422 (ラインドライバ)。<br>A/B/Z 相、1MHz (MAX) |  |

|        | 汎用入力                                      | TTL/オープンコレクタ                                 |  |

| メモリ    | DDR SDRAM 128MB                           |                                              |  |

| システムバス | PCI Express (× 4 レーン)                     |                                              |  |

| 外形寸法   | 168mm × 107mm                             |                                              |  |

**APX-3312**

### PCI Express Bridge LSI シリーズ

Gen 3

Gen 2

Gen 1

Gen 2 AAE-B24

Rev2.0 PCI Express x 4 (実効帯域:16Gbps) DDR-2

Local 64b/266Mbps  $+ \alpha$

Gen 3 AAE-B34

Rev3.0 PCI Express x 4 (実効帯域:32Gbps) DDR-3

Local ??

2007

Gen 1

AAE-B04

Rev1.0 PCI Express x 4 (実効帯域:8Gbps) DDR400 Local 64b/133Mbps

2009

2011

### まとめ

- ●設計負担低減

- PCI Expressを熟知しなくても良い。ユーザーロジックに専念できる。

- ドライバーサンプルの公開

- ●信頼性

- コンプライアンステスト PASS

- ●性能

- PCI Express アドインカードの性能を100%引き出す『仕掛け』

- ●機能の充実

- FPGAコンフィグレーション

- I2C /GPSIO/GPIO

- 内蔵メモリ

- ●今後の展開

- Gen2 Gen3 へのアプローチ

# http://www.avaldata.co.jp

ありがとうございました。

### AAE-B04のアイパターン